1. 컴퓨터의 기본 구조

컴퓨터는 프로그램 코드들을 정해진 순서대로 실행한다.

이 과정에서 데이터를 읽고(Read), 처리(Processing)하고, 저장(Store)한다.

CPU

프로세서(Processor)라고 불리기도 하며, 컴퓨터의 두뇌이다.

컴퓨터의 성능은 CPU의 성능과 직결된다고 볼 수 있다.

32-bit, 64-bit 컴퓨터도 분류되는 이유도 CPU가 한 번에 처리할 수 있는 비트 수에 따라서 나눈것이다.

주기억장치(main-memory)

우리가 알고 있는 RAM과 ROM이 주기억장치에 속한다. 메인보드상에서 CPU와 가까이 위치하며 빠른 읽기, 빠른 쓰기 속도를 가진다. 하지만 가격이 비싸고 면적을 많이 차지하며 적은 저장 용량을 가진다는 단점이 있다. 따라서 CPU가 프로그램을 실행하기 위해서 빠르게 가져올 코드나 데이터를 저장하는 장소로 사용된다.

보조저장장치

HDD나 SSD와 같이 용량이 크고 영구적으로 저장이 가능한 저장장치를 의미한다. 저장밀도가 높고 비트당 가격이 저렴하지만, 읽고 쓰는데 복잡한 반도체 기술을 이용하기 때문에 속도가 느리다. 그리고 보조저장장치는 CPU가 직접 엑세스하지 못하고, 별도의 제어기를 통해서만 가능하다.

입출력 장치(I/O 디바이스)

키보드, 모니터 등의 장치이다. 유저와 컴퓨터가 소통하기 위한 장치들이다. 별도의 제어기를 통해 CPU와 연결된다.

2. 정보의 표현과 저장

컴퓨터는 프로그램 코드를 통해 정보를 처리하고 데이터를 가공한다. 이러한 정보와 데이터는 모두 2진수로 이루어진다. 컴퓨터가 사용하는 프로그램은 C, C++, Python, Java와 같은 High-level 언어(고급 언어)를 이용하여 작성된다. 이렇게 작성된 프로그램은 컴퓨터가 읽을 수 없기 때문에 컴파일러라고 부르는 소프트웨어에 의해서 하드웨어가 이해할 수 있는 언어로 번역된다. 이때 하드웨어의 언어를 기계어 또는 기계 코드라고 한다.

하지만 모든 CPU가 같은 기계어를 가지고 있지 않기 때문에 언어상의 차이를 해소하기 위해서 High-level 언어들은 그들과 기계어의 중간 단계인 어셈블리어로 번역이 된다. 그리고 어셈블리어는 CPU에 맞는 기계어로 번역이 되면서 CPU는 명령을 수행할 수 있게 될 것이다.

어셈블리 명령어

LOAD A, X : 기억장치 X번지의 내용을 읽어서 레지스터 A에 담아라

ADD A, Y : 기억장치 Y번지의 내용을 읽어서 레지스터 A에 있는 값과 더하고, 결과를 레지스터 A에 담아라.

STOR Z, A : 레지스터 A의 내용을 기억장치 Z번지에 저장하라.

위 코드에서 LOAD, ADD, STOR 같은 기호를 니모닉스(mnemonics)라고 부른다.

명령어에는 CPU가 수행할 동작 + 처리할 데이터가 있는 주소값 + 레지스터 번호까지 구체적으로 적힌다.

이렇게 어셈블리어로 번역된 고급 언어는 어셈블러(assembler)라는 소프트웨어가 기계어로 번역해준다.

어셈블리 -> 기계어

LOAD A, X -> 00100101

| 연산코드 | 오퍼랜드 |

| 001 | 00101 |

연산코드 필드에 저장된 001은 '값을 레지스터 A에 담아라'는 연산을 지정해주는 비트이다.

오퍼랜드 필드의 00101은 값이 저장된 기억장치의 주소값을 가리킨다. 위 기계어에서는 오퍼랜드가 레지스터 5번지를 가리킨다고 볼 수 있다.

위 예제에서는 명령어가 기계어로 번역되었을 때 8bit로 나타난다.

이는 CPU에 의해 한 번에 처리될 수 있는 비트가 8bit라는 뜻이다. 따라서 CPU의 word(단어)는 8bit가 된다.

3.1 시스템의 구성

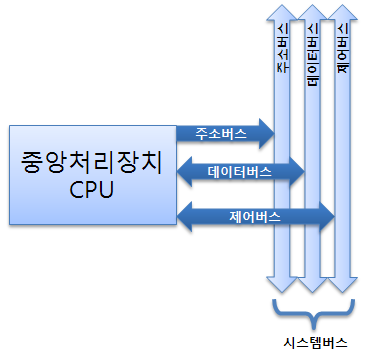

주소 버스(address bus)

주소 버스는 일정한 메모리 번지를 찾는 데 사용되는 신호를 운반하는 컴퓨터 내의 통로이다.

간단히 말해 물리 주소를 지정하는 데 쓰인다고 한다.

주소 버스의 폭은 시스템이 할당할 수 있는 메모리의 양을 결정한다. 만약 32비트 주소 버스를 지닌 시스템은 unsigned_int(2^32 = 4,294,967,296)개의 메모리 위치를 할당할 수 있다. 따라서 할당 가능한 메모리 공간은 4 GiB가 된다.

주소는 CPU에 의해 할당되어 기억장치와 I/O장치로 보내지는 정보이기 때문에, 주소 버스는 단방향이다.

데이터버스

CPU가 기억장치나 I/O디바이스간에 데이터를 전송하기 위한 통로이다. 데이터 버스의 폭은 한 번에 전송될 수 있는 데이터 비트의 수를 결정해준다. 예를 들어 데이터 버스가 32bit라면 CPU는 기억장치로부터 한 번에 32bit씩 읽어올 수 있다.

데이터는 읽기와 쓰기 동작이 모두 필요하므로 데이터버스는 양방향이다.

제어버스

CPU가 시스템 내의 각종 요소들의 동작을 제어하는데 필요한 통로이다.

기본적인 제어 신호로는 기억장치 읽기/쓰기, I/O읽기, 쓰기 등이있다.

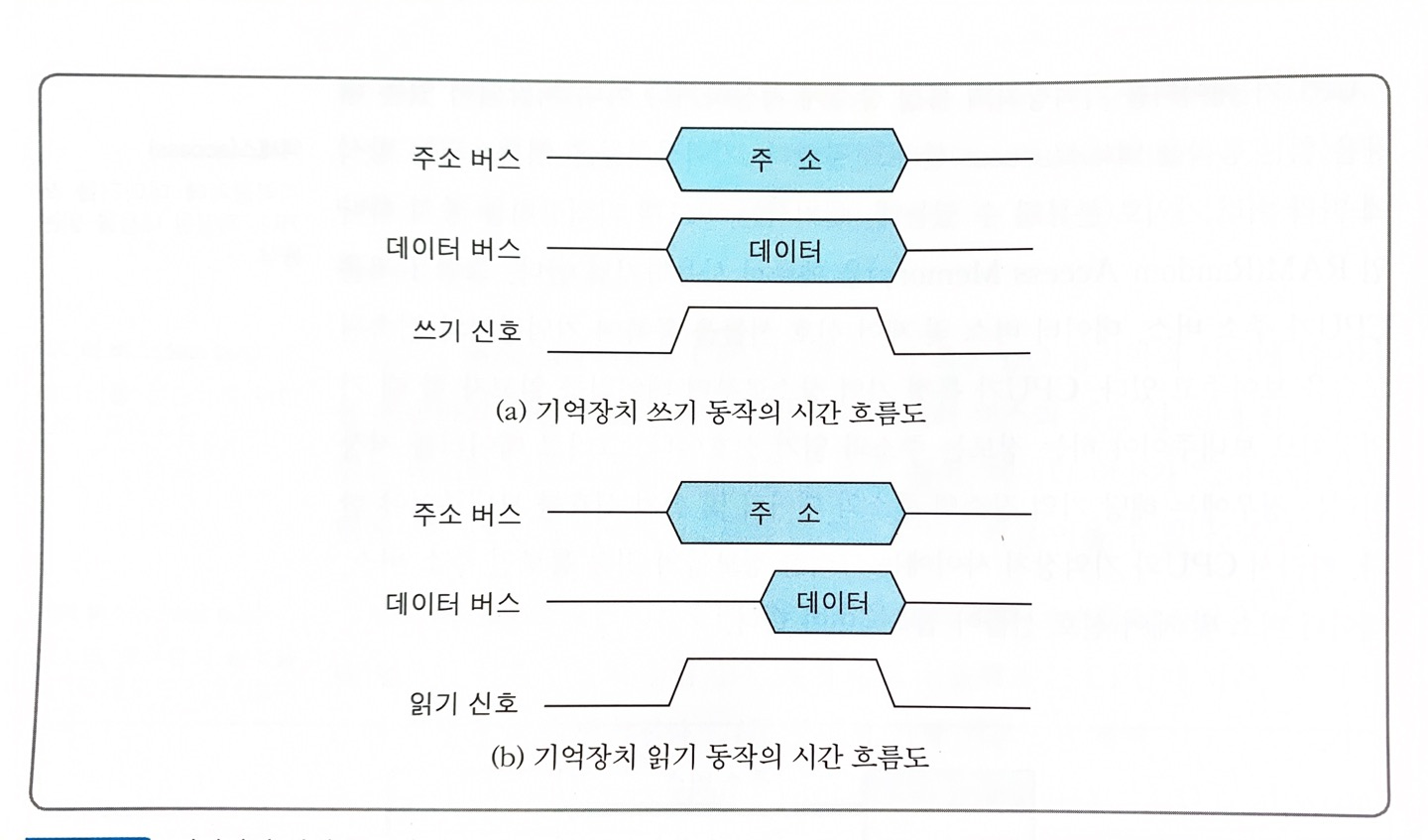

- 데이터 쓰기 동작 : CPU는 데이터를 저장할 기억 장소의 주소와 저장할 데이터를 각각 주소 버스와 데이터버스로 보내면서 동시에 쓰기 신호를 활성화시킨다. 신호들은 기억장치의 쓰기 동작이 완료될 때까지 유지되어야 한다. CPU가 주소와 데이터를 보낸 순간부터 기억장치에서 저장이 완료될 때까지의 시간을 기억장치 쓰기 시간이라고 한다.

- 데이터 읽기 동작 : CPU는 데이터가 저장된 주소를 보내면서 읽기 신호를 활성화시킨다. 일정 지연 시간이 흐른 후에 기억장치로 부터 읽은 데이터가 데이터 버스를 통해서 CPU로 전달된다. 지연시간이란 주소를 해독하고 기억장치 내부에서 데이터를 추출하는데 걸리는 시간이다. CPU가 주소를 보낸 시간부터 읽기 동작이 완료될 때까지의 시간을 기억장치 읽기 시간이라고 한다.

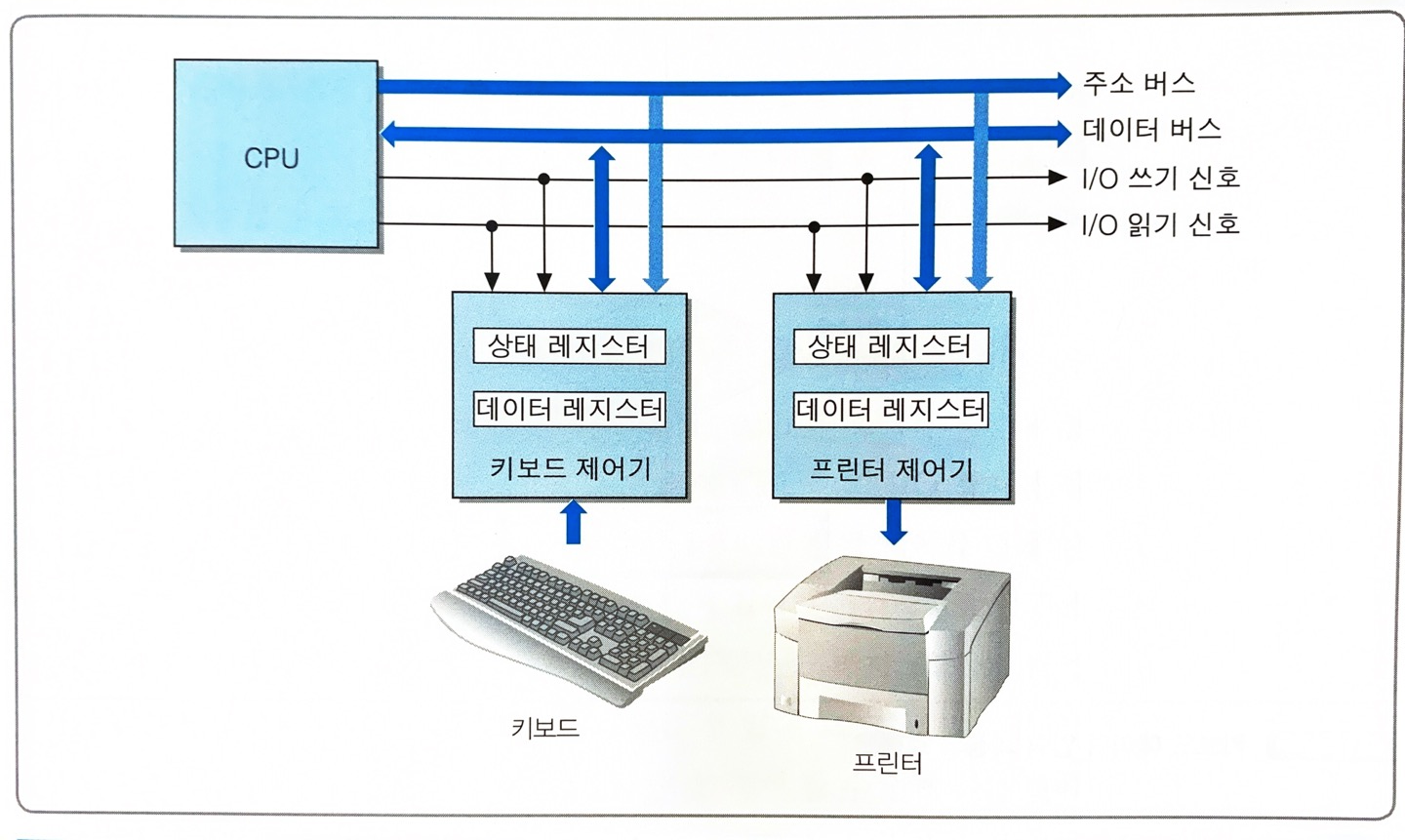

3.2 CPU 장치와 I/O장치의 접속

CPU가 키보드로부터 데이터를 읽어 들이는 과정

- 키보드의 키가 눌러진다.

- 키에 대응되는 아스키코드값 + 패리티 비트가 키보드 제어기로 전송된다.

- 전송된 키보드값이 데이터 레지스터에 저장되고, 동시에 상태 레지스터의 지정된 비트가 설정된다. 이때 입력 준비(In_RDY)라는 뜻의 비트로 설정된다.

- CPU가 데이터를 가져오고 싶을 때 상태 레지스터를 확인하고, In_RDY값이 1일 때 데이터 레지스터에 저장된 값을 가져온다.

- 만약 In_RDY값이 1이 아니라면 상태 레지스터 값을 확인하는 작업을 반복한다.

위 과정에서 데이터 레지스터는 CPU와 I/O 디바이스 사이에서 임시 저장장소 역할을 하기 때문에 데이터 버퍼라고 부르기도 한다.

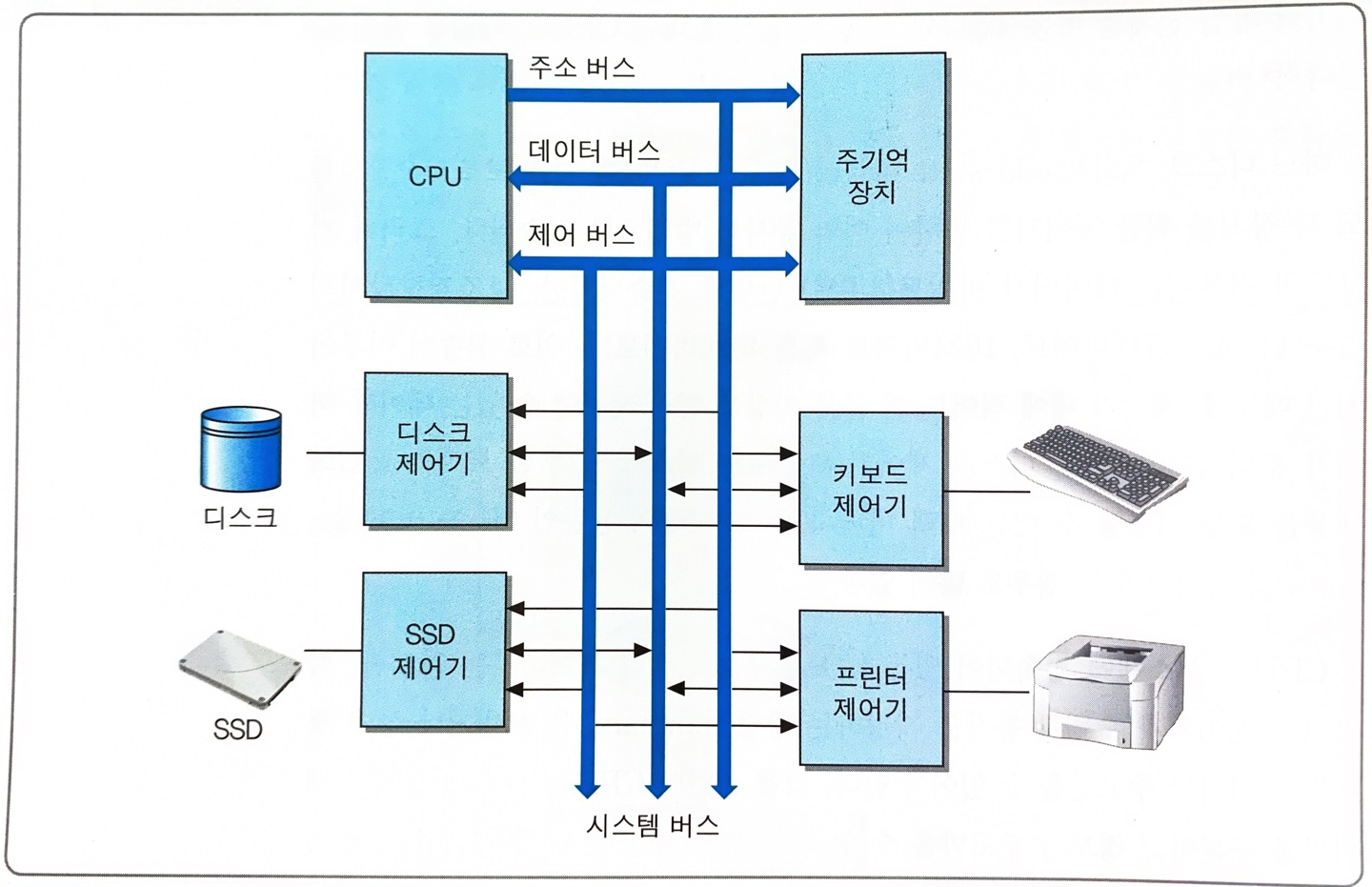

3.3 전체 시스템 구성

- 프로그램 실행 : CPU가 주기억장치로부터 프로그램 코드를 읽어서 실행한다.

- 데이터 저장 : 프로그램 실행 결과로서 얻어진 데이터를 주기억장치에 저장한다.

- 데이터 이동 : 디스크나 SSD에 저장되어있는 프로그램 코드나 데이터 블록을 주기억장치로 이동한다.

- 데이터 입력 및 출력 : 사용자가 키보드를 통해서 입력한 데이터를 읽어들인다. 모니터를 통해 결과를 출력한다.

- 제어 : 프로그램이 순서대로 실행되도록 혹은 필요에 따라 실행순서를 변경하도록 조정하며, 각종 제어신호들을 발생시킨다.

* 폰 노이만 구조

폰 노이만의 핵심 설계 개념은 다음과 같다

- 2진수 체계를 사용한다.

- 프로그램과 데이터를 내부에 저장한다.

위 설계 개념은 현대의 모든 컴퓨터의 기본 개념이 되었다.

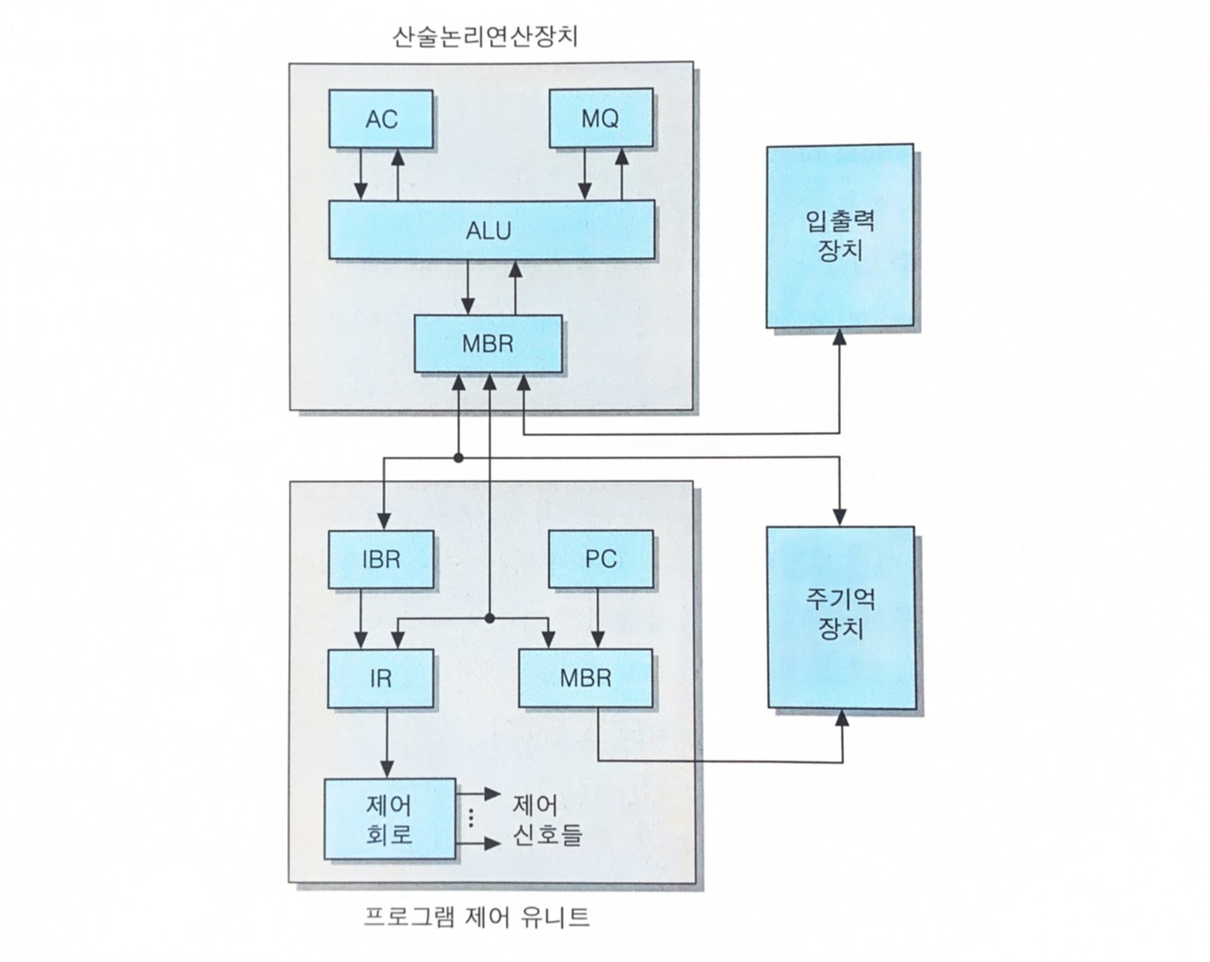

폰 노이만 구조를 사요한 IAS 컴퓨터 구조는 다음 그림과 같다.

ALU : 산술논리연산장치

MBR : 메모리 버퍼 레지스터

PC(Program Counter) : 다음번에 실행할 명령어의 주소를 가지고있다.

IR(Instruction Register) : MBR에 있는 명령어를 가져와서 decoding 해준다.

- 프로그램 제어 유니트는 주기억장치로부터 명령어들을 가져와서 IAS를 작동시킨다. (주기억장치로부터 한 번에 읽어오는 명령어는 2개씩이다.)

- 하나의 명령어는 즉시 프로그램 제어 유니트로 보내져 실행된다.

- 다른 하나는 명령어 버퍼(MBR)에 저장되어 있다가 다음 명령어 실행 사이클에서 실행된다. (이는 현대 컴퓨터에서 사용되는 명령어 선인출(instruction prefetch)와 유사한 방식이다.)

'CS > Computer Architecture' 카테고리의 다른 글

| [컴퓨터 구조] 산술 연산(덧셈, 곱셈) (0) | 2021.12.04 |

|---|---|

| [컴퓨터 구조] 산술 연산 (Shift) (2) | 2021.12.01 |

| [컴퓨터 구조] Addressing Mode (0) | 2021.06.12 |

| [컴퓨터 구조] Instruction Set (0) | 2021.06.12 |

| [컴퓨터 구조] Control Unit (0) | 2021.06.06 |